# **Future Technology Devices International Ltd.**

# Application Note AN\_118 Migrating Vinculum Designs From VNC1L to VNC2-48L1A

**Document Reference No.: FT\_000159**

Version 1.3

Issue Date: 2011-05-13

The purpose of this document is to provide guidelines for migrating VNC1L designs to VNC2.

| 1 | Introduction                                                 |    |  |  |  |  |

|---|--------------------------------------------------------------|----|--|--|--|--|

| 2 | 2 VNC1L vs VNC2                                              |    |  |  |  |  |

| 3 | Reference Schematics                                         | 4  |  |  |  |  |

|   | 3.1 VNC1L schematic                                          | 4  |  |  |  |  |

|   | 3.2 VNC2-48L1A Equivalent of VNC1L VDIP2 Reference Schematic | 5  |  |  |  |  |

| 4 | BOM Change required to convert from VNC1L to VNC2-48L1A 6    |    |  |  |  |  |

| 5 | 5 Firmware                                                   | 7  |  |  |  |  |

| 6 | S Loading Firmware                                           | 8  |  |  |  |  |

| 7 | Z Summary                                                    |    |  |  |  |  |

| 8 | Contact Information1                                         |    |  |  |  |  |

| A | Appendix A – SPI Clarification                               | 15 |  |  |  |  |

| Δ | Appendix B – Revision History                                | 16 |  |  |  |  |

Migrating Vinculum Designs From VNC1L to VNC2-48L1A Application Note AN\_118

Version 1.3

Clearance No.: FTDI# 139

### Introduction 1

The Vinculum VNC2 is FTDI's  $2^{nd}$  generation USB host controller solution and it expands on the capabilities of the VNC1L. VNC2 is supplied in 6 different packages. These are 32 pin QFN and LQFP packages, 48 pin QFN and LQFP packages and 64 pin QFN and LQFP packages.

The smaller packages reduce the number of IO by 16 pins to allow for more compact designs where space limitations are a consideration.

The larger packages provide additional 16 I/O to allow for increased functionality. In addition to the increased number of VNC2 package options, there is also a new software development tool suite developed by FTDI to enable users to create their own customised firmware.

The main focus of this document will be on how to migrate from a design using the VNC1L to a VNC2-48L1A device.

Clearance No.: FTDI# 139

# 2 VNC1L vs VNC2

The main features of the two generations of devices are shown below. All features are available in the 64 pin packages. The 48 pin and 32 pin packages have the same memory and internal functions but less I/O. The 48 pin package matches the VNC1L device. For full details see the VNC2 Datasheet at www.ftdichip.com

| FEATURE                         | VNC1L                           | VNC2                         |

|---------------------------------|---------------------------------|------------------------------|

|                                 |                                 |                              |

| MECHANICAL                      | 12 1 1 2 2                      |                              |

| Package                         | 48 pin LQFP                     | 64, 48,32 pin QFN or LQFP    |

| Temperature                     | -40 to +85C                     | -40 to +85C                  |

| ELECTRICAL                      |                                 |                              |

| VCC                             | 3V3                             | 3V3                          |

| VCCIO                           | 5V tolerant 3V3                 | 5V tolerant 3V3              |

| CLK source                      | 12MHz (external)                | 12MHz (external)             |

| СРИ                             | 8-bit Harvard architecture      | 16-bit Harvard architecture  |

| INTERFACING                     |                                 |                              |

| USB ports                       | 2                               | 2                            |

| UART port                       | 1                               | 1                            |

| SPI slave port                  | 1                               | 2                            |

| SPI master port                 | 0                               | 1                            |

| FIFO monitor port option        | 1                               | 1                            |

| Debug port                      | 0                               | 1                            |

| FIRMWARE                        |                                 |                              |

| Precompiled firmware            | YES                             | YES                          |

| Tools for creating own firmware | NO                              | YES                          |

| MEMORY                          |                                 |                              |

| DATA RAM                        | 4k x 8 (4kbytes)                | 4k x 32 (16kbytes)           |

| E-FLASH                         | 64k x 8 (64kbytes)              | 128k x 16 (256kByte)         |

| USB MODES                       |                                 |                              |

| Speed                           | Full / low                      | Full / low                   |

| Transfer modes                  | Bulk / Interrupt                | Bulk, interrupt, isochronous |

| CONFIGURATION PORTS             |                                 |                              |

| UART                            | YES                             | YES                          |

| USB                             | YES (after initial programming) | YES                          |

| SPI                             | NO                              | YES                          |

| FIFO                            | NO                              | YES                          |

| DEBUG PORT                      | N/A                             | YES                          |

|                                 |                                 |                              |

|                                 |                                 |                              |

Clearance No.: FTDI# 139

# 3 Reference Schematics

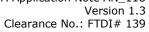

# 3.1 VNC1L schematic

This schematic is for the VDIP2 based on the VNC1L.

Clearance No.: FTDI# 139

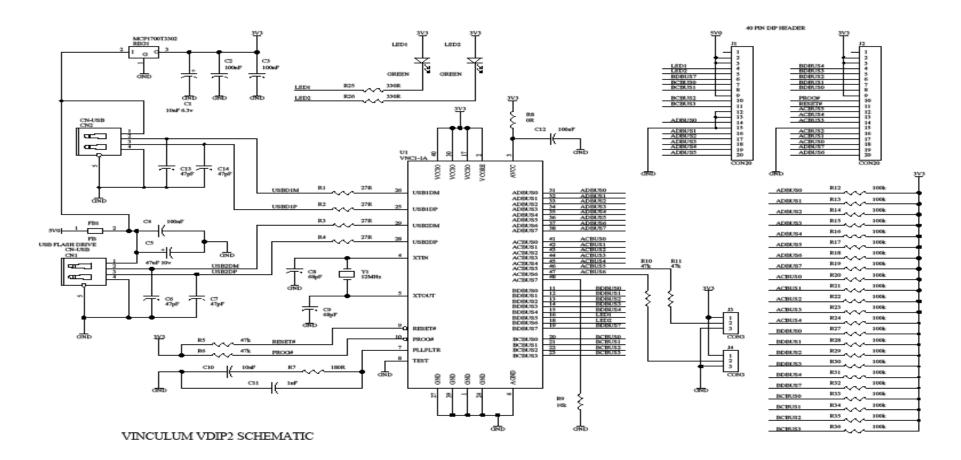

# 3.2 VNC2-48L1A Equivalent of VNC1L VDIP2 Reference Schematic

Clearance No.: FTDI# 139

# 4 BOM Change required to convert from VNC1L to VNC2-48L1A

| VNC1L Schematic<br>Component | VNC2-48L1A Schematic<br>Component                            | Description                        |

|------------------------------|--------------------------------------------------------------|------------------------------------|

| U1 - VNC1L                   | U1 -VNC2-48L1A                                               | Controller IC                      |

| C8, C9 – 68pF Capacitor      | C10, C11 – 27pF Capacitor                                    | Load capacitor on crystal          |

| R9, 10k resistor             | Do not fit pull down on U1 pin 48                            | PLL enable                         |

| R7, 180R                     | Replace with 0R link or simply track over if redesigning PCB | VNC1L PLL Filter / VNC2<br>VREGOUT |

| C10, 10nF                    | C12, 4.7uF                                                   | VNC1L PLL Filter / VNC2<br>VREGOUT |

| C11, 1nF                     | C13, 100nF                                                   | VNC1L PLL Filter / VNC2<br>VREGOUT |

| R8, 0R to 3V3                |                                                              | Remove                             |

|                              |                                                              |                                    |

The pull up resistors, shown on the VNC1L schematic R12-R36, are optional even on the VNC1L schematic.

Pin 3 AVCC of the VNC2-48L is internally bonded to the 1V8 internal regulator. This is the only package with this internal bond for ease of upgrade from a VNC1L.

FTDI Chip

Version 1.3

Clearance No.: FTDI# 139

# 5 Firmware

As the internals of the two devices is different, the firmware that runs on the devices is different. However to maintain backward compatibility there is equivalent firmware available for download.

| VNC1L Firmware | VNC2 Firmware |

|----------------|---------------|

| VDAP           | V2DAP         |

| VMSC           | V2MSC         |

| VDPS           | V2DPS         |

| VCDC           | V2CDC         |

| VDIF           | V2DIF2        |

These builds may be downloaded from <a href="www.ftdichip.com">www.ftdichip.com</a> (at the time of writing this application note, some of these builds were not available, but were scheduled to be put onto the website soon).

In addition to using these pre-compiled libraries, VNC2 is supplied with a software development tool chain to allow customers to customise the pre-compiled firmware or create their own firmware for greater flexibility in design.

Note: The precompiled builds are designed for the 48 pin pkg as that was all VNC1L was available in.

VNC2-48L1A Application Note AN $\_118$ Version 1.3

Clearance No.: FTDI# 139

# 6 Loading Firmware

VNC1L was limited to using the UART to load firmware onto a blank device. The VNC2 may be programmed via the debug port or via the UART interface. Although FTDI will provide utilities for this, there may be situations where users prefer to develop their own programmer over the UART and there are some significant differences between VNC1L and VNC2.

Key differences between VNC1L and VNC2:

- Each block of the flash on the VNC2 is 128 bytes compared with 64 bytes on the VNC1L.

- The endianess of the VNC2 is different from that of the VNC1L meaning that data must be reversed before it can be sent to the device.

- The size of the ROM files on VNC1L were all 64k, the ROM files on the VNC2 can be anything up to the size of the flash.

To program the VNC2 firmware over the UART the device must be reset in prog mode; this is achieved by driving the **prog#** pin low and then driving the **reset#** pin low then high. When the device is in prog mode it is ready be programmed over the UART using the following command / response standard.

| Command<br>Name | Command(s):         | Response     | Comment                                                                                 |

|-----------------|---------------------|--------------|-----------------------------------------------------------------------------------------|

| Echo            | 0xFF                | 0xFF         |                                                                                         |

| Echo            | 0xFB                | 0xFB         | VNC1L used the 0xFA command to echo, VNC2 uses 0xFB to distinguish between the devices. |

| Set Baud        | 0x01                | 0x02         | (115200 Baud == 1, 1 MBaud == 2, 3 MBaud == 3)                                          |

| Rate            | BaudRate(1, 2 or 3) |              |                                                                                         |

| Read Address    | 0x02                | 0x02         |                                                                                         |

|                 | FlashAddrLow        | Data to Read |                                                                                         |

|                 | FlashAddrHigh       |              |                                                                                         |

| Write Address   | 0x03                | 0x02         | The 0x02 response will be sent after FlashAddrHigh has                                  |

|                 | FlashAddrLow        |              | been received by the device.                                                            |

|                 | FlashAddrHigh       |              |                                                                                         |

|                 | Data to Write       |              |                                                                                         |

Below is a snippet of the test code that has been used to write and verify the flash of the VNC2....

```

// Sample code for writing flash of VNC2 written in C/C++.

// Function: sendData - writes the data read from the ROM file to the VNC2 and verifies it.

// Parameters: romfile - a handle to the ROM file obtained from the open(....) function.

filename - a char array containing the name of the rom file that we have opened.

//

ftHandle - handle to the TTL cable that we are communicating over.

//

// Return:

returns 1 on successful completion, !1 otherwise.

char sendData(int romfile, char *filename, FT_HANDLE ftHandle)

{

unsigned long filesize;

unsigned long pageSegCount;

// The amount of pages needed to store the ROM file.

unsigned long pageRem = 0;

// Portion of a ROM file left over that doesn't fill a full

unsigned long numwrit;

// Not required to be used....

unsigned long padByteCnt = 0;

unsigned long padSegRem = 0;

unsigned long padSegSize = (1 * 128);

unsigned char databuf[PAGESIZE];

// Data read from the ROM file.

```

Clearance No.: FTDI# 139

```

// Data read from the ROM file reversed to accommodate

unsigned char endianBuf[PAGESIZE];

// VNC2 endianess

unsigned char receiveBuf[PAGESIZE]; // Data received from the VNC2

unsigned char j = 0;

unsigned char cmd;

unsigned char dataread = 0x00;

unsigned char baudbuf[6];

FT_STATUS ftStatus;

unsigned long i;

// Index used as the location within the device flash.

struct stat stbuf;

stat(filename, &stbuf);

// FILE SIZE CALCULATIONS

filesize = stbuf.st size;

pageSegCount = filesize / PAGESIZE;

pageRem = filesize % PAGESIZE;

//echo from the device...

cmd = 0xFF;

ftStatus = FT_Write(ftHandle, &cmd, 1, &numwrit);

numwrit = 0;

ftStatus = FT Read(ftHandle, &dataread, 1, &numwrit);

cmd = 0xFB;

ftStatus = FT Write(ftHandle, &cmd, 1, &numwrit);

numwrit = 0;

ftStatus = FT_Read(ftHandle, &dataread, 1, &numwrit);

// Set the baud rate of the chip...

cmd = 0x01;

baudbuf[0] = cmd;

// 1, 2 or 3

baudbuf[1] = 0x03;

ftStatus = FT_Write(ftHandle, baudbuf, 2, &numwrit);

// Allow some time for the baud rate to settle...

Sleep(100);

// Set the baud rate of the TTL cable.

FT_SetBaudRate(ftHandle, 3000000);

numwrit = 0:

ftStatus = FT_Read(ftHandle, &dataread, 1, &numwrit);

if(dataread != 0x02)

printf("The baud rates aren't synced, exiting.\n");

return -1;

}

//echo from the device...

cmd = 0xFB:

FT_Write(ftHandle, &cmd, 1, &numwrit);

numwrit = 0;

FT Read(ftHandle, &dataread, 1, &numwrit);

cmd = 0xFF;

FT_Write(ftHandle, &cmd, 1, &numwrit);

numwrit = 0;

FT_Read(ftHandle, &dataread, 1, &numwrit);

printf("Writing File");

// Increment by one to accommodate the fractional page, the fractional page will be memset with

// 0xFF...

```

Clearance No.: FTDI# 139

```

pageSegCount++;

for(i = 0; i < pageSegCount; i++)</pre>

unsigned char transdata[2];

int numread = 0;

// Memset the data buffer...

memset(databuf, 0xFF, PAGESIZE);

numread = read(romfile, databuf, PAGESIZE);

// Change the data to little? endian for VNC2.

for (j=0; j < PAGESIZE; j += 2)

endianBuf[j] = databuf[j+1];

endianBuf[j+1] = databuf[j];

}

WRITE FORMAT

0x03

FlashAddressLow

FlashAddressHigh

Data block to write.

cmd = 0x03;

FT_Write(ftHandle, &cmd, 1, &numwrit);

transdata[0] = (i \& 0xFF);

transdata[1] = ((i >> 8) \& 0xFF);

// Send the data address....

FT_Write(ftHandle, transdata, 2, &numwrit);

// Check for a response from this....

FT Read(ftHandle, &dataread, 1, &numwrit);

if(dataread != 0x02)

{

printf("!");

return -1;

}

// Send the data.

// Send the data address....

FT Write(ftHandle, endianBuf, PAGESIZE, &numwrit);

// Check for a response again....

FT_Read(ftHandle, &dataread, 1, &numwrit);

if(dataread == 0x02)

{

printf(".");

}

else

printf("!");

return -1;

}

READ FORMAT

0x02

FlashAddressLow

FlashAddressHigh

// Read the data back to make sure that it has been programmed correctly.

```

Clearance No.: FTDI# 139

```

cmd = 0x02;

transdata[0] = (i \& 0xFF);

transdata[1] = ((i >> 8) \& 0xFF);

// Send the command

FT Write(ftHandle, &cmd, 1, &numwrit);

// Send the data address....

FT_Write(ftHandle, transdata, 2, &numwrit);

// Check for a response from this....

FT_Read(ftHandle, &dataread, 1, &numwrit);

Sleep(10);

// Make sure that we have 128 bytes to read from the chip!!!

FT GetQueueStatus(ftHandle, &numwrit);

if(numwrit < PAGESIZE)</pre>

{

printf("Not enough data to read");

return -1;

}

// Read 128 bytes back from the chip...

FT_Read(ftHandle, receiveBuf, PAGESIZE, &numwrit);

// Compare the data read back from the flash with the data sent....

// NOTE: The data that is returned is reversed due to the endianess of the VNC2,

// compare the returned data with the data that we reversed to send to the chip.

for(j = 0 ; j < PAGESIZE; j++)

if(endianBuf[j] != receiveBuf[j])

printf("The data returned is not the same!");

return -1;

}

}

return 1;

}

```

Document Reference No.: FT\_000159

Migrating Vinculum Designs From VNC1L to VNC2-48L1A Application Note AN\_118

Version 1.3

Clearance No.: FTDI# 139

# 7 Summary

In summary VNC2 will allow for existing PCBs to be upgraded to the more powerful device without needing to change the PCB, but will also allow for greater customisation of the firmware and hence a better product and user experience.

New designs, requiring new PCBs may also opt for different device packages. The 32 pin option will allow for smaller designs where space is a consideration. The 64 pin package will allow for additional functionality to be added via the extra pin count.

FTDI Chip

Version 1.3

Clearance No.: FTDI# 139

### 8 Contact Information

# Head Office - Glasgow, UK

Future Technology Devices International Limited Unit 1, 2 Seaward Place, Centurion Business Park Glasgow G41 1HH United Kingdom

Tel: +44 (0) 141 429 2777 Fax: +44 (0) 141 429 2758

E-mail (Sales) <a href="mailto:sales1@ftdichip.com">sales1@ftdichip.com</a>

E-mail (Support) <a href="mailto:support1@ftdichip.com">support1@ftdichip.com</a>

E-mail (General Enquiries) <a href="mailto:admin1@ftdichip.com">admin1@ftdichip.com</a>

Web Site URL <a href="http://www.ftdichip.com">http://www.ftdichip.com</a> Web Shop URL <a href="http://www.ftdichip.com">http://www.ftdichip.com</a>

### Branch Office - Taipei, Taiwan

Future Technology Devices International Limited (Taiwan)

2F, No 516, Sec. 1 NeiHu Road

Taipei 114 Taiwan, R.O.C.

Tel: +886 (0) 2 8797 1330 Fax: +886 (0) 2 8751 9737

E-mail (Sales) <u>tw.sales1@ftdichip.com</u>

E-mail (Support) <u>tw.support1@ftdichip.com</u> E-mail (General Enquiries) <u>tw.admin1@ftdichip.com</u>

Web Site URL <a href="http://www.ftdichip.com">http://www.ftdichip.com</a>

### Branch Office - Hillsboro, Oregon, USA

Future Technology Devices International Limited (USA) 7235 NW Evergreen Parkway, Suite 600 Hillsboro, OR 97123-5803 USA

Tel: +1 (503) 547 0988 Fax: +1 (503) 547 0987

E-Mail (Sales)

E-Mail (Support)

E-Mail (General Enquiries)

Web Site URL

us.sales@ftdichip.com

us.support@ftdichip.com

us.admin@ftdichip.com

http://www.ftdichip.com

### Branch Office - Shanghai, China

Future Technology Devices International Limited (China) Room 408, 317 Xianxia Road, ChangNing District, ShangHai, China

Tel: +86 (21) 62351596 Fax: +86(21) 62351595

E-Mail (Sales): cn.sales@ftdichip.com E-Mail (Support): cn.support@ftdichip.com

E-Mail (General Enquiries): cn.admin1@ftdichip.com

Web Site URL: http://www.ftdichip.com

Document Reference No.: FT\_000159

Migrating Vinculum Designs From VNC1L to VNC2-48L1A Application Note AN $\_118$

Version 1.3

Clearance No.: FTDI# 139

# **Distributor and Sales Representatives**

Please visit the Sales Network page of the FTDI Web site for the contact details of our distributor(s) and sales representative(s) in your country.

Neither the whole nor any part of the information contained in, or the product described in this manual, may be adapted or reproduced in any material or electronic form without the prior written consent of the copyright holder. This product and its documentation are supplied on an as-is basis and no warranty as to their suitability for any particular purpose is either made or implied. Future Technology Devices International Ltd will not accept any claim for damages howsoever arising as a result of use or failure of this product. Your statutory rights are not affected. This product or any variant of it is not intended for use in any medical appliance, device or system in which the failure of the product might reasonably be expected to result in personal injury. This document provides preliminary information that may be subject to change without notice. No freedom to use patents or other intellectual property rights is implied by the publication of this document. Future Technology Devices International Ltd, Unit 1, 2 Seaward Place, Centurion Business Park, Glasgow G41 1HH United Kingdom. Scotland Registered Number: SC136640

FTDI Chip

Version 1.3

Clearance No.: FTDI# 139

# **Appendix A - SPI Clarification**

There is a subtle difference in the SPI mode of operation between VNC1L and VNC2 in VNC1L SPI backward compatible mode.

In essence VNC1L waits for the chip select line to go active and then the start bit must be a '1' for the transaction to begin.

In VNC2 backward compatibility mode the chip waits for the chip select to go active and then counts the next 12 clocks as the full transmission. The start bit is effectively a don't care state.

If the SPI interface is accessed by the external controller (master) by bit-banging the SPI bits of the interface there will be no new problems.

If the SPI interface is accessed by the external controller using its in-built 8-bit wide SPI interface and simply padding with 0's either at the front or the end of the message it will not work.

As such the interface must be bit-banged to ensure it works with VNC1L and VNC2 in this mode. The first bit after the chip select is active must be the start bit. No padding is allowed.

Clearance No.: FTDI# 139

# **Appendix B - Revision History**

Version PreliminaryFirst Preliminary version available1st Feb 2010Version 1.0First release Rev 1.0 available19th Feb 2010Version 1.1Added new chapter 6 for loading firmware over UART22nd March 2010Version 1.2Modified chapter 622nd April 2010Version 1.3Correction to write opcode in section 6<br/>Added appendix A13th May 2011